首先介紹疊層封裝技術的發展現狀及最新發展趨勢 , 然后采用最傳統的兩層疊層封裝結構進行分析 , 包括描述兩層疊層封裝的基本結構和細化兩層疊層封裝技術的 SMT組裝工藝流程。最后重點介紹了目前國際上存在并投入使用的六類主要的疊層封裝方式范例 , 同時進一步分析了疊層封裝中出現的翹曲現象以及溫度對翹曲現象的影響。分析結果表明 :由于材料屬性不同會引起正負兩種翹曲現象;從室溫升高到 150 ℃左右的時候易發生正變形的翹曲現象, 在 150 ℃升高至 260 ℃的回流焊溫度過程中多發生負變形的翹曲現象。

隨著半導體制造技術以及立體封裝技術的不斷發展 , 電子器件和電子產品對多功能化和微型化的要求越來越高。在這種小型化趨勢的推動下 , 要求芯片的封裝尺寸不斷減小。根據國際半導體技術路線圖 (ITRS), 三維疊層封裝技術能更好的實現封裝的微型化 。三維疊層封裝具有如下特點 :封裝體積更小 , 封裝立體空間更大, 引線距離縮短從而使信號傳輸更快, 產品開發周期短投放市場速度快等。疊層封裝主要應用在移動手機、 手提電腦、數碼相機等手持設備和數碼產品中。三維疊層封裝主要分為三種形式:載體疊層 、 裸芯片疊層和晶圓疊層。3D裸芯片疊層封裝技術主要有多芯片封裝 (multi-chippackaging, MCP)、內置封裝技術(package-in-package,PiP)和 疊 層 封 裝 技 術(package-on-package, PoP)。本文主要介紹疊層封裝。PoP就是在一個處于底部的封裝件上再疊加另一個與其相匹配的封裝件 , 組成一個新的封裝整體。PoP的各封裝件之間相對比較獨立 , 同時能對底部和頂部的封裝器件進行單獨測試, 以保證其滿足預先設定的參數和良好的性能, 這樣更能滿足KGD (knowngooddie)的要求 , 有較高的器件封裝良品率。由于 PoP封裝的獨立性表現在保證各封裝體測試過關的前提下可以將不同廠商的封裝器件堆疊匹配封裝在一起, 所以器件的選擇也具有更大的自由靈活性 , 這是 PoP工藝的最大優勢。同時在PoP封裝中即使出現了問題 , 也可以拆開來單獨檢修、測試 , 因而堆疊封裝技術 PoP成為主要的 3D封裝技術 。最簡單的 PoP封裝包含兩個疊層裸芯片, 具體實例有日本的堆疊式內存 , 這種堆疊式內存結構由含有一個閃存和一個 SRAMM內存的雙裸片組 成的;目前, 疊層 密 度最 高 的實 例 是Samsung公司應用于 3G手機的 6層疊層存儲芯片;同時作為引線鍵和疊層方式的擴展 , ASE公司在疊層封裝中使用了引線鍵合和倒裝鍵合相結合的混合鍵合的封裝方式。

疊層封裝技術經過近十年的時間, 已經發展得十分成熟。疊層封裝器件分為兩類 :一類是存儲器與存儲器堆疊在一起;另一類是底層為邏輯器件而頂層為存儲器件。最典型的疊層封裝技術 PoP的封裝模型由圖 1所示。

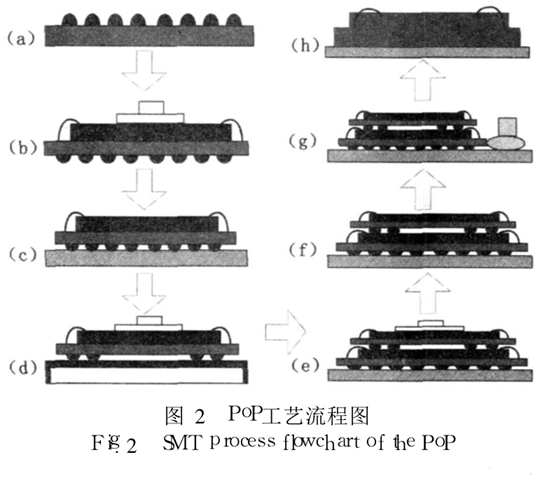

最簡單的 PoP模型是兩層堆疊模型 , 除此之外還有多層堆疊模型。一般簡單的兩層堆疊模型組成結構是分為上下兩部分 , 即底部和頂部 , 而且底部和頂部的封裝器件功能是不同的。通常情況下底部的封裝件是一個高集成度的邏輯器件, 頂部的封裝件是一大容量的存儲器或存儲器件組合。多層堆疊封裝體的結構與簡單疊層封裝體結構相比, 不同之處在于其頂部可以是多個具有存儲功能的存儲器封裝器件。由綜上所述可以看出疊層封裝技術 PoP的出現已經模糊了封裝與組裝的界線。本文以最簡單的兩層疊層封裝技術為例介紹其 SMT封裝流程 ,其封裝流程圖如圖 2所示 。在進行 PoP的 SMT封裝之前首先要對非 PoP面元件進行組裝, 其中的工藝流程包括傳統的絲網印刷、 貼片、回流和檢測 。然后再進行 PoP面元件的組裝。疊層封裝技術 PoP的 SMT工藝流程如圖 2所示。

圖 2中 : (a)圖為首先利用表面貼裝技術在封裝基板上貼裝元件如電阻、電容等; (b)圖為然后拾取 PoP底部封裝器件; (c)圖為將底部封裝器件放置在基板上, 進行貼裝 ; (d)圖為在頂部基板上涂覆助焊劑; (e)圖為將頂部封裝器件放置在底部封裝器件上;(f)圖為對整體封裝器件進行回流焊接; (g)圖為對 PoP封裝體進行底部填充; (h)圖為對 PoP封裝體的底部填充進行固化 , 從而完成 PoP的 SMT封裝。

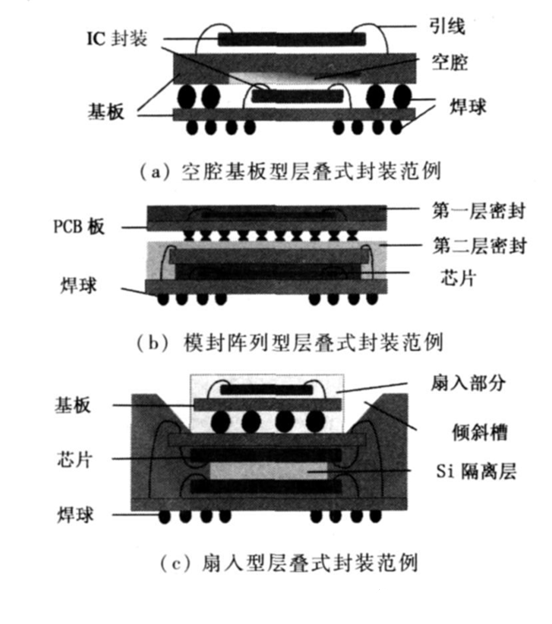

由于 PoP封裝技術能更好地實現封裝的微型化 , 并且具有如下特點:封裝體積更小, 封裝立體空間更大, 引線距離縮短從而使信號傳輸更快 , 產品開發周期短投放市場速度快等, 所以被廣泛地應用在移動手機、手提電腦 、數碼相機等手持設備和數碼產品中 。國際上關于 PoP封裝技術的專利有幾十種, 主要分為以下七類 :常規疊層式封裝、帶中空式轉接板的層疊式封裝 、帶覆蓋式轉接板的層疊式封裝 、空腔基板型層疊式封裝、 模封陣列型層疊式封裝、 模料穿孔型層疊式封裝和扇入型層疊式封裝。各類封裝范例如圖 3所示。

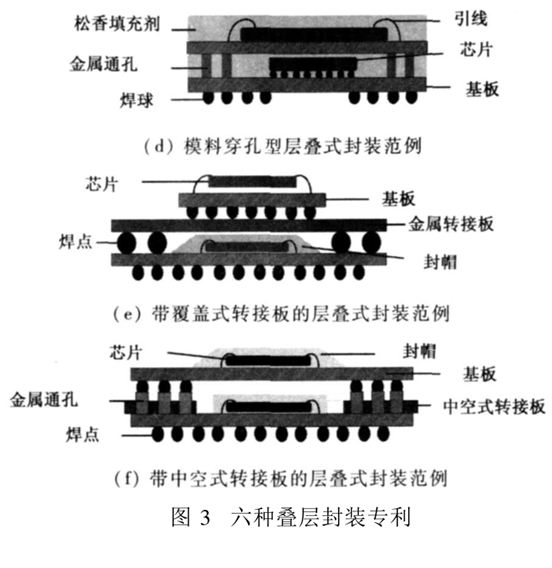

PoP封裝面臨的最嚴重的可靠性問題是翹曲現象。習慣上將翹曲現象根據形狀定義如下:若翹曲形狀為向上凸則稱之為正變形, 若翹曲形狀為向下凹就稱之為負變形 , 如圖 4所示。

影響翹曲因素主要是封裝基板和芯片的材料屬性 , 包括熱膨脹系數 CTE和彈性模量。在室溫和回流焊溫度下材料屬性對疊層封裝翹曲現象的影響是不同的, 如圖 5所示。

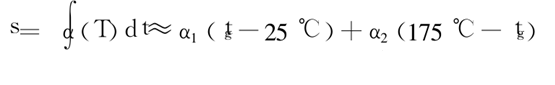

由圖 5可以看到在室溫下條件下隨著彈性模量和熱膨脹系數的變化 , 翹曲數值都基本為正, 表現為向上凸的正變形;而在回流焊高溫條件下隨著彈性模量和熱膨脹系數的變化, 翹曲數值都為負數 ,表現為向下凹的負變形。目前改善疊層封裝PoP翹曲現象的研究主要包括結構優化、材料選擇和工藝優化三個方面。封裝結構一般包括硅芯片 、 塑封材料和基板三部分, 其中硅芯片和基板之間的熱膨脹系數不匹配是引起翹曲現象的主要原因。在由室溫升高到回流焊溫度又由高溫逐漸冷卻到室溫的溫度變化過程中 , 會產生化學收縮和熱收縮現象 , 由此而導致翹曲現象。塑封料作為中間介質可以起到補償作用 。塑封料中一般都含有超過80%的填充材料, 填充材料比例越大化學收縮值就會越小。而熱收縮值由下面的等式決定。

式中:α表示熱膨脹系數 ;tg 表示玻璃轉換溫度。由公式 (1)可知 , 減小α可以減小熱收縮值 。所以在封裝工藝中經常采用減小熱膨脹系數的方法來降低翹曲現象。

另外還可以通過減小芯片尺寸大小和減薄芯片厚度來增大塑封料的比例 , 進而降低翹曲現象。常采用的芯片減薄方法有研磨、 深反應離子刻蝕法(DRIE)和化學機械拋光法 (CMP)等工藝, 通常減薄至 50 μm左右 , 目前減薄技術可將圓片減薄 10至 15 μm, 為確保電路的性能和芯片的可靠性, 圓片減薄的極限為 20 μm左右, 否則會影響存儲器的性能。直接減薄芯片厚度, 產生的殘余應力會影響存儲器的性能。此時可以利用晶圓拋光技術來釋放應力, 增強芯片的健壯性。

在滿足電子產品更快數字信號處理、 更大存儲容量、成本更低 、體積更小的要求, 尤其在堆疊復雜邏輯器件和存儲器器件方面, PoP是一種上市時間短、 成本低的疊層封裝解決方案。除了綜上所述的可靠性問題, 疊層封裝方案還存在著一些缺陷, 例如由于芯片尺寸不匹配而導致的線鍵合過程中的引線過長 , 就會增加引線鍵合工藝的難度和成本, 還可能會由于后道塑封工序的工藝問題出現金線沖彎、短路 、脫球等現象 , 從而導致封裝產品的失效 ;由于引線鍵合過程中的布線密度比較高, 極易出現引線短路, 導致引線鍵合工藝失敗;若相鄰芯片的間距過小而無法進行引線鍵合, 則可能導致封裝失敗。這些工藝缺陷都是疊層封裝面臨的挑戰 , 亟待解決。