眾所周知,隨著5G的商業化演進,射頻前端模塊的設計越來越復雜,越來越多的不同工藝的裸片將集成到一個封裝模塊中,集成化小型化的需求導致設計的流程越來越復雜,并且需要滿足的指標越來越多,要求越來越高。而激烈的競爭環境導致設計工程師需要加速每一個設計環節從而實現產品的快速迭代與上市。這就導致了無論從電路仿真還是物理設計上,都對EDA工具提出了更高的要求。

就RF前端模塊封裝物理設計來講,目前國內流行的設計流程已經不能滿足這樣的需求。而作為一名射頻前端模塊設計工程師,需要應付不同的工藝設計標準,采用不同的供應商作為不同工藝以及不同封裝基板的生產加工。但由于現有EDA工具某些功能的不完備以及缺失,尤其是關于封裝基板的設計,不同于IC的設計標準,封裝廠或者基板廠不會提供相應的與EDA工具對標的DRC文件作為設計工程師檢驗的標準。設計工程師需要根據封裝廠或者基板廠商提供的相關規則自己通過寫一些腳本甚至肉眼檢查是否合規。這就大大加大了出錯的概率,從而需要與基板廠商尤其是封裝廠商進行來來回回的溝通反復修改迭代,極大的延后了投板時間,延長了設計周期,降低了設計效率。

同時,對于傳統的RF封裝設計工具來講,一些關于封裝、裸片、SMD的footprint及相關的邊框文字等,以及一些用戶定義的VIA尺寸與形式,大多數需要工程師通過腳本以及手動去描畫。這也極大地降低了工程師的設計效率,延遲了投板時間。

綜上所述,我將為大家帶來RF設計攻略第一期內容——“如何提高RF前端模塊封裝設計的迭代效率”線上培訓。從射頻前端模塊的物理設計出發,結合應用實例分享,希望給大家帶來不一樣的設計體驗,也希望各位有經驗的設計同仁提出你們的寶貴意見。

為了能使更多的設計同仁參與到培訓內容,本系列培訓將采用線上直播的形式,通過手機端和電腦端的方式與大家進行交流互動。

講到這里可能有的工程師會問到,如果只有射頻前端封裝的物理設計而沒有仿真,我們也無法檢驗設計是否能滿足我們的要求。因此,我們將在下一期培訓中著重介紹整個RF設計流程,從物理設計到合規檢查,從電磁場熱場仿真到電路仿真。同時還可以實現從芯片、封裝到PCB電路板的協同設計與仿真。具體內容請見日后通知。

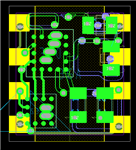

“RF設計攻略第一期:如何提高RF前端模塊封裝設計的迭代效率”線上培訓中的實例演示部分將采用Cadence Allegro? SiP工具。作為Allegro在封裝設計端的產品,SiP工具延續了Allegro本身的設計布局風格,包括各種自動化footprint生成、自動化布局布線以及規則檢查的功能。這些功能在滿足封裝用戶本身對設計全面化、自動化等需求的基礎上,更加入了各種定制化的RF器件布局與設計,從各個方面滿足了RF前端模塊設計工程師的多重物理設計需求。